在現代開關(guan) 電源設計中,同步整流技術因其高效率和低損耗而被廣泛應用。LP20R100C是一款高性能的高壓合封同步整流芯片,適用於(yu) 多種開關(guan) 電源控製係統,能夠顯著提高電源的轉換效率。本文將詳細介紹LP20R100C的規格參數及其內(nei) 部框架結構,幫助設計工程師更好地理解和應用該芯片。

輸入電壓:LP20R100C支持高達100V的輸入電壓,適用於(yu) 多種高壓開關(guan) 電源應用。

電源電壓(VCC):工作電壓範圍為(wei) -0.3V至8V,確保在不同電源條件下穩定工作。

導通阻抗(RDS_ON):在VGS=6.5V和IDS=0.1A的條件下,導通阻抗為(wei) 17-20mΩ,低導通阻抗有助於(yu) 減少功率損耗。

連續電流(ID):在25℃環境下,連續電流為(wei) 40A,能夠承受較高的負載電流。

脈衝(chong) 電流(ID,pulse):在25℃環境下,脈衝(chong) 電流為(wei) 140A,適用於(yu) 瞬時高電流需求的應用場景。

開通電壓閾值(VON):-0.25V至-0.15V,確保同步整流管在適當的電壓下開通。

關(guan) 斷閾值(VOFF):-8mV至-2mV,準確判斷同步整流管的關(guan) 斷時機。

關(guan) 斷延遲時間(Td):25ns至33ns,快速關(guan) 斷有助於(yu) 提高係統效率。

VCC欠壓保護:當VCC電壓下降到3.8V至4.2V時,芯片進入欠壓保護狀態,防止因電源不穩定導致的損壞。

過壓鉗位:VCC鉗位電壓為(wei) 6.3V至6.7V,保護芯片不受過壓損害。

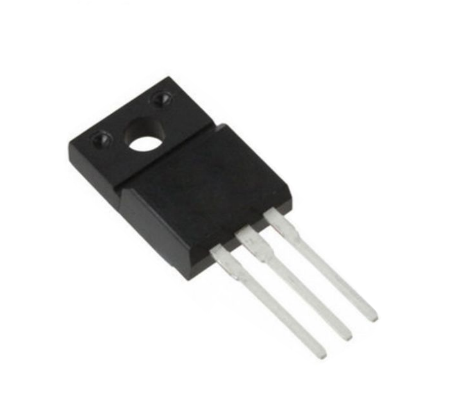

封裝形式

LP20R100C采用TO220-3L封裝,具有良好的散熱性能和機械強度,適合高功率應用。

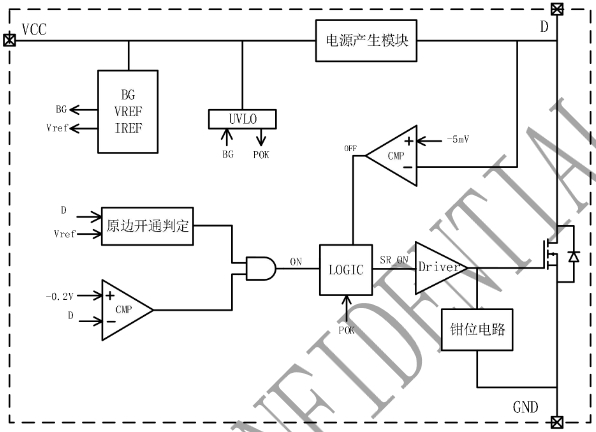

LP20R100C的內(nei) 部框架圖展示了其複雜的電路結構和功能模塊,主要包括以下幾個(ge) 部分:

VCC供電:芯片內(nei) 部集成了VCC供電技術,能夠在不需要輔助繞組供電的情況下,保證VCC電壓穩定.當係統上電後,通過內(nei) 置MOS的體(ti) 二極管對輸出電容充電,當VCC電壓達到開啟閾值時,芯片內(nei) 部控製電路開始工作。

開通控製:采用專(zhuan) 利的整流管開通技術,通過檢測漏極電壓(D腳)與(yu) 地(GND)之間的下降電壓閾值和下降速率,準確判斷同步整流管的開通時機.開通條件包括同步最小關(guan) 斷時間(TSR)大於(yu) 2us,開通檢測斜率(dVds/dt)大於(yu) 設定值,且Vds小於(yu) -0.2V。

關(guan) 斷控製:為(wei) 了避免因激磁振蕩導致的誤關(guan) 斷,LPSR100通過整流管關(guan) 斷閾值準確判斷關(guan) 斷時機.在比較器屏蔽時間(Tb)內(nei) 不進行關(guan) 斷動作,當Ton大於(yu) Tb且Vds電壓大於(yu) -5mV時,關(guan) 斷同步整流管。

欠壓保護:當VCC電壓低於(yu) 欠壓保護閾值時,芯片進入保護狀態,防止因電源不穩定導致的損壞。

過壓保護:通過VCC鉗位電路,將VCC電壓限製在安全範圍內(nei) ,防止過壓損害芯片。

內(nei) 置100V耐壓功率管,能夠在高電壓條件下穩定工作,提供高電流輸出。

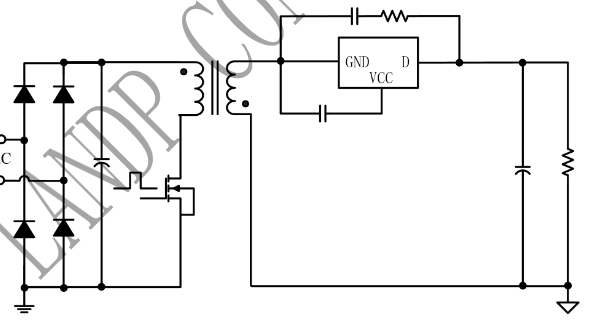

LP20R100C廣泛應用於(yu) 充電器、適配器、正激控製器和反激控製器等開關(guan) 電源控製係統中,具有以下優(you) 勢:

高效率:同步整流技術顯著提高了電源的轉換效率,降低了能量損耗。

低損耗:低導通阻抗和快速開關(guan) 特性減少了功率損耗,提高了係統的整體(ti) 性能。

高可靠性:多重保護功能確保芯片在各種工作條件下的穩定性和可靠性。

簡單設計:集成度高,外圍元器件少,簡化了電路設計,降低了設計複雜度和成本。

通過深入理解LP20R100C的規格參數和內(nei) 部框架結構,設計工程師可以更好地將其應用於(yu) 開關(guan) 電源設計中,提高產(chan) 品的性能和可靠性。